# 分子性金属酸化物を実装した FET 型メモリの基礎特性評価

宇部工業高等専門学校 藤林 将

Fundamental Characterization of FET-Type Memory Embedded with Metal-Oxide Molecules

### National Institute of Technology, Ube College

近年、分子性金属酸化物の一種である Preyssler 型ポリオキソメタレートが単分子で恰も強誘電体の様に振舞う「単分子誘電体」であることが報告された。この分子は一般的な強誘電体と異なり、分子一つ一つが不揮発性メモリとして駆動するポテンシャルを有するため、メモリ素子の圧倒的な高密度化が期待される。本研究では、「単分子誘電体」を実装した電界効果型トランジスタの開発に取り組み、不揮発性メモリとして駆動することを見出した。

Recently, the ferroelectric-like behavior within a single-molecule has been reported by using Preyssler-type polyoxometalates which is one of the metal-oxide molecules. This novel physical property in single-molecule was named "single-molecule electret (SME)". Unlike general ferroelectrics, each molecule has the potential to be driven as a nonvolatile memory, which is expected to lead to the application of ultra-high-density memory devices. In this study, we developed a field-effect transistor embedded with a SME and found that it can be driven as a non-volatile memory.

#### 1. 序論

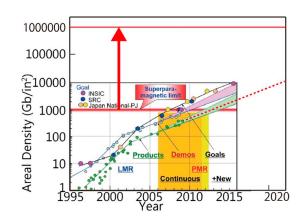

ビッグデータ活用や IoT 産業の活性化が進む中、大容量ストレージへの需要がますます高まっている。一方で、不揮発性メモリの記録密度は物理的限界を迎えると指摘されており、根本的な材料改良の面から代替材料の台頭が求められている【図1】。記録密度に限界値が存在する理由として、不揮発性メモリに不可欠な強的性質(強磁性や強誘電性)が結晶由来の物性であることが挙げられる。これらの材料は、結晶としての根幹となる長距離秩序を有する状態でのみ物性を発現するため、数原子・分子のオーダーでは特性が消失してしまい物理的な微細化限界を有している。

図1. 近年の記録密度の推移と、示唆されている物理的な記録密度の限界値、及び本研究での限界値。

この様な背景の中、研究代表者が2023年度まで所属していた広島大学固体物性化学研究室の西原教授は、この重要問題を打開し得る「単分子誘電体」の開発に世界で初めて成功した。[1]「単分子誘電体」は、従来の強誘電体理論を覆し、単一分子で強誘電体特有の分極

ヒステリシス(メモリ効果)を示すため、分子一つ一つに1bitの情報を格納させることができる。従って、この「単分子誘電体」をメモリ素子として実用化できれば、既存の記録密度限界を1000倍上回る新しいタイプのメモリデバイスを創出できる。本研究では同材料を用いたデバイス開発と材料改良に取り組み、「単分子誘電体」が不揮発性メモリとして駆動することを見出した。

# 2. 物性の発現機構

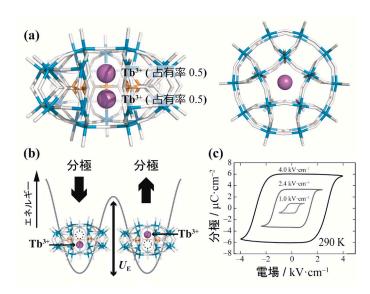

「単分子誘電体 は、世界に先駆け 広島大学で立証した真に新しい物理 現象であり、アニオン性の分子、プ レイスラー型ポリオキソメタレート  $(K_{12}[Tb^{3+} \subset P_5W_{30}O_{110}])$ を用いて 達成された【図2a】。この分子は、 籠型の分子骨格内部に中心からずれ た2箇所のイオン安定サイトを有し ており、ここに1つのテルビウムイ オン(Tb<sup>3+</sup>)が格納されている【図 2a 。従って、プラスの電荷を有す る Tb<sup>3+</sup> イオンがどちらかの安定サ イトに停止することで、分子内で電 荷の偏りが生じ分子分極が発現する 【図 2b】。サイト間のイオン移動(分 極反転)にエネルギー障壁が存在し ているとき、障壁よりも低温領域で はイオンの位置は固定され、分子分 極が凍結される【図 2b】。この温度

図 2. (a) 単分子誘電体の分子構造。分子内部には等価な 2 つの安定なイオンサイトが存在し、そこに 1 つの  $Tb^{3+}$  イオンが格納されている。(b) 2 つのサイト間 にはエネルギー障壁  $(U_E)$  が存在し、二極小ポテンシャル構造を形成している様子。(c) 「単分子誘電体」の分極 - 電場曲線。室温近傍で分極ヒステリシスが観測された。

域で電場を印加することでイオン移動が誘起され、分極反転を起こす。この一連の過程は単分子の中で完結するため、単分子で強誘電体に類似した分極ヒステリシスの発現が期待される。誘電率測定より、400 K 以下で明確な強誘電体 - 常誘電体転移が観測されなかった一方、分子内のイオン移動に由来する誘電分散が観測された。観測された誘電分散からアレニウスプロットを作成し、イオン移動が止まる温度(ブロッキング温度)を見積もったところ、286 K と算出された。この温度域で、分極の電場依存性測定や焦電流測定を行ったところ、強誘電体に特徴的な分極ヒステリシス【図 2c】や自発分極が観測された。以上の点より、この分子は結晶に特徴的な長距離秩序を伴わずに単分子で強誘電体の様に振舞う「単分子誘電体」であると結論付けられた。この「単分子誘電体」を不揮発性メモリとして実装すると、分子レベルまで微細化できる為、既存の記録密度限界を 1000 倍上回る超高密度不揮発性メモリを作製することが可能となる。

#### 3. 結果と考察

### 3-1. 電界効果型トランジスタ(FET)の作製

デバイス作製に先立ち、半導体レベルでのクリーン度を実現するため、陽イオン交換樹

| Element | Result    | ND     | Unit     | Result   | Unit |

|---------|-----------|--------|----------|----------|------|

| Si      |           |        |          | 2163.554 | cps  |

| Р       | 16961.066 | 42.426 | E10A/cm2 | 304.921  | cps  |

| S       | 3384.672  | 19.799 | E10A/cm2 | 97.099   | cps  |

| Tb      | 1019.144  | 0.566  | E10A/cm2 | 1325.931 | cps  |

| W       | 19263.717 | 3.960  | E10A/cm2 | 1084.967 | cps  |

Copyright © — Rigaku Corporation and its Global Subsidiaries. All Rights Reserved

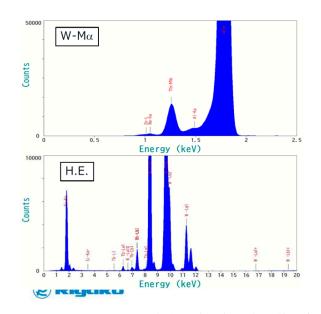

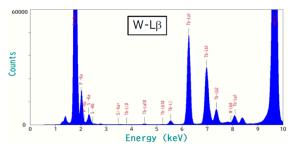

図3. 材料の全反射蛍光 X 線測定結果(Rigaku 社にて測定を実施)。

脂を用いた不純物イオンの除去と再結晶法による結晶精製を行った。[2] シリコンプロセスフローにおいて金属イオンなどの不純物が材料に混入している場合、不純物が酸化膜内に侵入し、デバイス特性に悪影響を与えることが知られている。そのため、実用化を見据えた際には、不純物濃度が 10<sup>10</sup> 個 /inch<sup>2</sup> 以下である必要がある。上述の通り、原料であるPreyssler 型ポリオキソメタレートには、カウンターカチオン(電荷中和に用いる陽イオン)としてカリウムイオンが含まれている。陽イオン交換樹脂を用いカリウムイオンを溶液中から除去することで、半導体プロセス上においてリーク要因として働かないイオン種へと交換し試料精製を実施した。精製後の試料を Si 基板上に塗布し、全反射蛍光 X 線測定より不純物濃度を測定した。測定結果より、構成元素以外(基板洗浄のため S 原子(硫酸由来)が検出されている)の不純物は観測されず、半導体レベルでクリーンな材料であることを証明した【図 3】。以降のトランジスタ工程では、改良した材料を用いた。

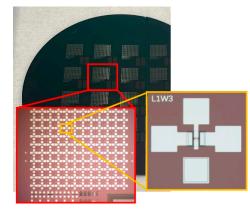

改良した材料を用いて作製した FET 型メモリの顕微鏡写真を【図 4】に示した。素子構造には微細化・実用化を見据え、FET 構造を採用した。FET では、ソース – ドレイン間チャネルに流れる電流をゲート電圧によりコントロールすることで、チャネルの ON/OFF を制御する。ゲート電極直下にはゲート絶縁膜として誘電体が挿入されており、一般的な誘

電体(例えばSiO<sub>2</sub>)を用いる場合、ゲート電圧が印加されている場合でのみチャネルのON/OFFを制御することが可能である。一方でゲート絶縁膜として強誘電体を用いることで、一度ゲート電圧を印加すれば電圧が印加された後の状態を強誘電体が記録し、不揮発性メモリとして駆動する可能である。本研究では、強誘電体の代わりとして「単分子誘電体」をゲート絶縁膜に採用し、不揮発性メモリの開発に取り組んだ。既存のC-MOSプロセスとの親和性を確保するため、ドライ・ウェットの両プロセスから検討を進めることで電界効果型トランジスタの作製

図4. 実際に作製したメモリデバイス の顕微鏡写真。

に成功した。今回、ゲート長(L)、ゲート幅(W)をマイクロオーダーで調整し、4 インチ p型 Si 基板内にメモリデバイスを作製した。p型 Si 基板内で通常のn-MOS を作製する工程に「単分子誘電体」の塗布工程を挿入することで素子の作製に成功した。この点で、塗布工程を追加するのみでトランジスタの作製を可能としており、実用化に向けた知見を得た。

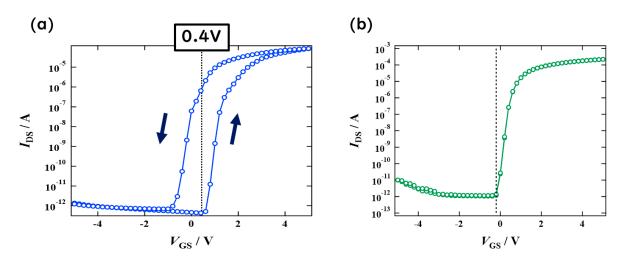

## 3-2. 電界効果型トランジスタ(FET)の特性評価

作製したメモリデバイスについて、トランジスタ特性( $V_{GS}-I_{DS}$ 、 $V_{DS}-I_{DS}$ )を評価した。 【図 5】には評価結果の抜粋として、 $L=10\,\mathrm{um}$ 、 $W=25\,\mathrm{um}$  に設計した素子について測定し た V<sub>cs</sub> - I<sub>Ds</sub> の評価結果を示した。また、比較として、「単分子誘電体」を含まないトラン ジスタについても併せて示した【図 5b】。尚、 $V_{DS}$  は 0.1V に固定した。一般的な n-MOS型 FET の  $V_{GS}$  –  $I_{DS}$  測定では、ドレイン・ゲート両電圧にプラスの電圧を印加することで トランジスタを ON 状態にすることが可能であり、ゲート電圧の掃引によってトランジス タの ON/OFF を制御することが可能である。【図 5a】の測定結果を比較したところ、「単 分子誘電体」を実装した素子にのみ、 $V_{GS}$ の掃引に対する  $V_{DS}$ の履歴現象(メモリウィンド ウ)が観測された。ここでメモリウィンドウとは不揮発性メモリでのみ観測される特異な 現象であり、一度閾電圧を超えてオープン状態になったチャネルが ON 状態の閾電圧以下 で OFF 状態になることを意味している。【図 5b】に示したように揮発性メモリとして駆動 するトランジスタでは、メモリウィンドウは存在せず、往路と復路の電流挙動(Ips)は同 じ履歴をたどる。この点で、「単分子誘電体」がメモリとして駆動していることが明らかに なり、本研究の最終目標である「単分子誘電体」のメモリ特性評価を達成した。加えて、  $V_{GS} = 0.4 \text{ V}$  (【図 5a】中黒点線) における ON/OFF 比は 10 $^{6}$  乗程度であることが分かり、一 般的なトランジスタと比較しても良好な性質を示した。現在は素子構造の更なる改良を推 進しており、微細化・集積化の両観点からデバイス開発を継続している。

図 5.  $V_{GS}$ - $I_{DS}$  評価結果。(a)「単分子誘電体」を実装した素子、(b) 同様のプロセスで作製した「単分子誘電体」を含まない素子、の評価結果。

#### 4. 結論

本研究では単分子で強誘電体の様に振舞う「単分子誘電体」を実装した FET 型メモリの 開発に取り組んだ。初段階として、半導体プロセスに適合可能な材料へと改良を行い、Si 半導体プロセス上でリーク源となり得るカリウムイオンの除去に成功した。改良した材料を用いてFET型メモリの作製に着手したところ、既存の半導体プロセスに親和性を有するプロセスによって素子開発に成功し、作製した素子が不揮発性メモリとして駆動することを明らかにした。本研究を通して、「単分子誘電体」メモリの実用化に向けた初動研究を達成することに成功した。

#### 5. 謝辞

本研究は、令和3年度日本板硝子材料工学助成会の研究助成を受けておこなったものである。同助成会に心より感謝いたします。

# 6. 参考文献

- [1] C. Kato, S. Nishihara, et al., Angew. Chem. Int. Ed., 2018, 57, 13429-13432.

- [2] A. Hayashi, S. Nishihara, M. Sadakane, et al., ACS Omega, 2018, 3, 2363-2373.